# ASSP For Power Supply Applications

# Mobile Pentium<sup>®</sup> II DC/DC Converter IC

# **MB3871**

### DESCRIPTION

The FUJITSU MB3871 is a pulse width modulation (PWM) DC/DC converter IC chip that provides a selection of 1.3 V to 2.0 V output voltages for Mobile Pentium<sup>®</sup> II\* CPU's, using a 4-bit input signal information.

The MB3871 utilizes synchronous rectification for high efficiency and features a soft-start/discharge control function for ease in designing power supplies in multi-supply systems, making it ideal for Mobile Pentium<sup>®</sup> II power supply systems.

\* : Pentium is the registered trademark of Intel Corporation.

### FEATURES

- Highly efficient for using synchronous rectification scheme

- On-chip soft-start/discharge control circuit

- High precision output voltage: ±1.2%

- 4-bit, 16-step DAC: 2.0 V to 1.3 V in 50 mV steps

- Frequency range: 100 kHz to 500 kHz using variable resistance (on-chip frequency setting capacitance)

- Standby current: 0 μA TYP

- · On-chip PWRGOOD circuit for output voltage state detection

- · Timer-latch short-circuit protection circuit, and overvoltage protection circuit for output protection

#### PACKAGE

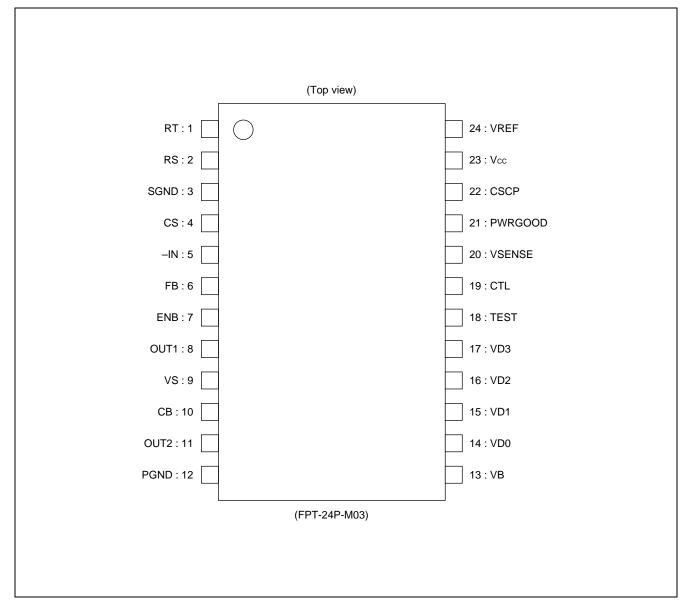

# ■ PIN ASSIGNMENT

## ■ PIN DESCRIPTION

| Pin no. | Symbol  | I/O | Descriptions                                                                                                                              |

|---------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RT      | _   | Triangular wave frequency setting resistor connection pin                                                                                 |

| 2       | RS      | _   | Discharging resistor connection pin for soft start capacitor                                                                              |

| 3       | SGND    | _   | Ground pin                                                                                                                                |

| 4       | CS      | _   | Soft start capacitor connection pin (Also used for discharge control)                                                                     |

| 5       | -IN     | I   | Error amplifier inverted input pin                                                                                                        |

| 6       | FB      | 0   | Error amplifier output pin                                                                                                                |

| 7       | ENB     | I   | Discharge control function enable/disable switch control pin                                                                              |

| 8       | OUT1    | 0   | Totem-pole output pin (External main-side FET gate drive)                                                                                 |

| 9       | VS      | _   | External main-side FET source-side connection                                                                                             |

| 10      | СВ      | —   | Output bootstrap pin<br>Insert a capacitor between the CB and VS pins, to bootstrap the IC internal<br>output transistor.                 |

| 11      | OUT2    | 0   | Totem-pole output pin (External synchronous rectifier-side FET gate drive)                                                                |

| 12      | PGND    | _   | Ground pin                                                                                                                                |

| 13      | VB      | _   | Output circuit power supply pin                                                                                                           |

| 14      | VD0     | I   | 4-bit digital input pin used to set DC/DC converter output voltage                                                                        |

| 15      | VD1     | I   | 4-bit digital input pin used to set DC/DC converter output voltage                                                                        |

| 16      | VD2     | Ι   | 4-bit digital input pin used to set DC/DC converter output voltage                                                                        |

| 17      | VD3     | Ι   | 4-bit digital input pin used to set DC/DC converter output voltage                                                                        |

| 18      | TEST    | —   | Test pin for D/A output. Set to open when in use.                                                                                         |

| 19      | CTL     | I   | Power supply control pin<br>The CTL pin is set to "L" level to place the IC in standby mode.                                              |

| 20      | VSENSE  | I   | PWRGOOD circuit input pin                                                                                                                 |

| 21      | PWRGOOD | 0   | PWRGOOD output pin (open-drain output)<br>Outputs a "H" level signal when the output voltage is within the range from<br>VTLOW to VTHIGH. |

| 22      | CSCP    | _   | Timer-latch short-circuit protection capacitor connection pin                                                                             |

| 23      | Vcc     | _   | Power supply pin for reference power and control circuit                                                                                  |

| 24      | VREF    | 0   | Reference voltage output pin                                                                                                              |

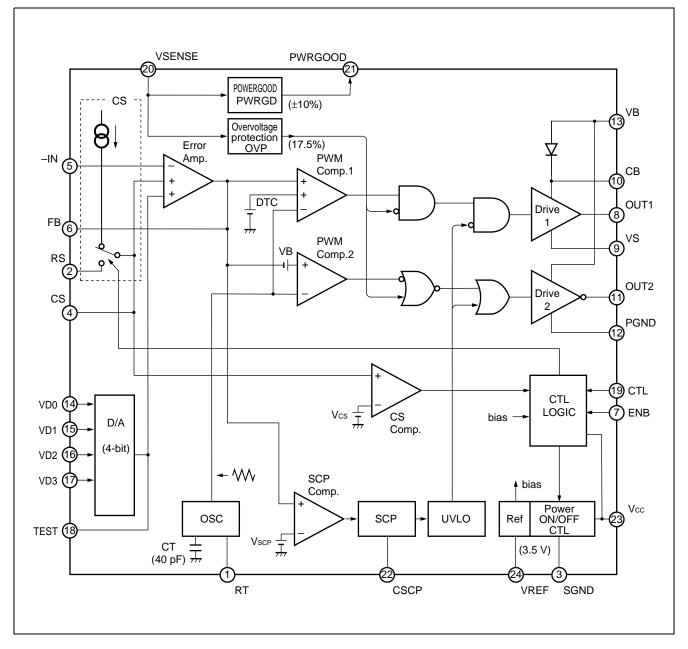

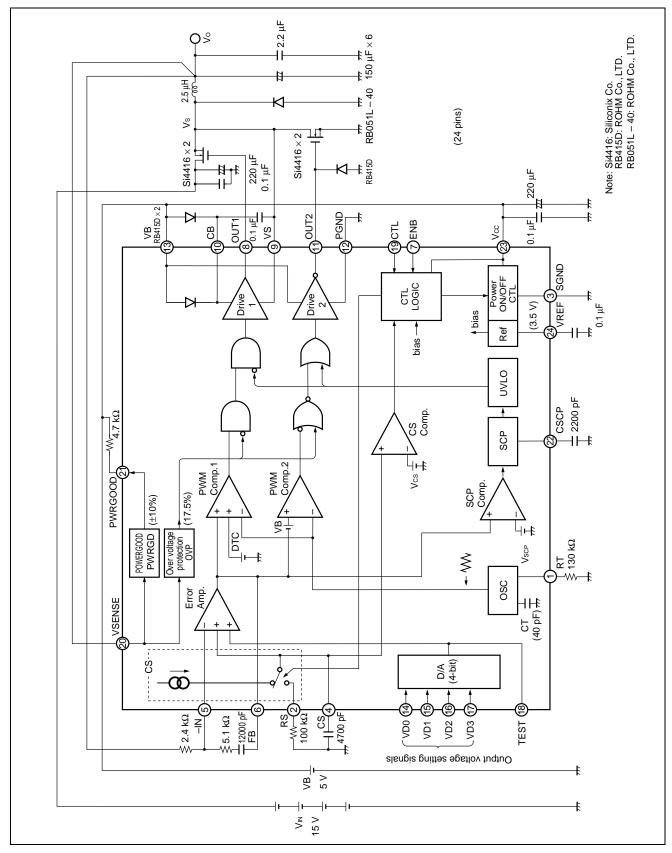

## ■ BLOCK DIAGRAM

# ■ OUTPUT VOLTAGE SETTING CODE

| VD3 | VD2 | VD1 | VD0 | Output voltage setting (V) |

|-----|-----|-----|-----|----------------------------|

| 0   | 0   | 0   | 0   | 2.000                      |

| 0   | 0   | 0   | 1   | 1.950                      |

| 0   | 0   | 1   | 0   | 1.900                      |

| 0   | 0   | 1   | 1   | 1.850                      |

| 0   | 1   | 0   | 0   | 1.800                      |

| 0   | 1   | 0   | 1   | 1.750                      |

| 0   | 1   | 1   | 0   | 1.700                      |

| 0   | 1   | 1   | 1   | 1.650                      |

| 1   | 0   | 0   | 0   | 1.600                      |

| 1   | 0   | 0   | 1   | 1.550                      |

| 1   | 0   | 1   | 0   | 1.500                      |

| 1   | 0   | 1   | 1   | 1.450                      |

| 1   | 1   | 0   | 0   | 1.400                      |

| 1   | 1   | 0   | 1   | 1.350                      |

| 1   | 1   | 1   | 0   | 1.300                      |

| 1   | 1   | 1   | 1   | 0 (output OFF)             |

# ■ ABSOLUTE MAXIMUM RATINGS

| Parameter              | Symbol | Condition                          | Value       | Unit |

|------------------------|--------|------------------------------------|-------------|------|

| Power supply voltage   | Vcc    | —                                  | 20          | V    |

| Bias voltage           | Vв     | —                                  | 20          | V    |

| Boot voltage           | Vсв    | —                                  | 32          | V    |

| Control input voltage  | Vctl   | —                                  | 20          | V    |

| PWRGOOD output voltage | Vpwrgd | —                                  | 17          | V    |

| Output current         | lo     | —                                  | 120         | mA   |

| Peak output current    | lo     | Duty $\leq$ 5% (t = 1/fosc × Duty) | 800         | mA   |

| Allowable dissipation  | PD     | Ta ≤ +25°C                         | 740*        | mW   |

| Storage temperature    | Tstg   | _                                  | -55 to +125 | °C   |

\* : When mounted on a 10 cm-square dual-sided epoxy base board

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# ■ RECOMMENDED OPERATING CONDITIONS

| Deveryoter                           | Cymhal | Condition                             |      | Unit |           |      |

|--------------------------------------|--------|---------------------------------------|------|------|-----------|------|

| Parameter                            | Symbol | Condition                             | Min. | Тур. | Max.      | Unit |

| Power supply voltage                 | Vcc    | —                                     | 4.6  | 5    | 18        | V    |

| Bias voltage                         | Vв     | —                                     | _    | 5    | 18        | V    |

| Boot voltage                         | Vсв    | —                                     | _    | _    | 30        | V    |

| Reference voltage output current     | lor    | _                                     | -1   |      | 0         | mA   |

|                                      | Vin    | –IN pin                               | 0    | _    | Vcc - 0.9 | V    |

| Input voltage                        | VIN    | CTL, ENB,<br>VD3 to VD0 pins          | 0    | — 18 |           | V    |

|                                      | Vin    | VSENSE                                | 0 —  |      | Vcc       | V    |

|                                      | lo     | OUT pin                               | -100 | _    | 100       | mA   |

| Output current                       | IPG    | PWRGOOD pin                           | _    | —    | 1         | mA   |

| Peak output current                  | lo     | Duty $\leq$ 5%<br>(t = 1/fosc × Duty) | -700 | _    | 700       | mA   |

| Oscillator frequency                 | fosc   | —                                     | 100  | 200  | 500       | kHz  |

| Timing resistance                    | R⊤     | —                                     | 51   | 130  | 270       | kΩ   |

| Boot capacitance                     | Св     | —                                     | _    | 0.1  | 1.0       | μF   |

| Reference voltage output capacitance | Cref   | _                                     | _    | 0.1  | 1.0       | μF   |

| Soft start capacitance               | Cs     | —                                     | _    | 4700 | 10000     | pF   |

| Discharge control resistance         | Rs     | —                                     | —    | 100  | 470       | kΩ   |

| Short detection capacitance          | CSCP   | —                                     | —    | 2200 | 10000     | pF   |

| Operating temperature                | Та     | —                                     | -30  | +25  | +85       | °C   |

# WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.

# ■ ELECTRICAL CHARACTERISTICS

(Ta = +25°C, Vcc = 5 V)

| _                         |                                             | Pin              |       |                                                  | Value  |        |        | ,    |

|---------------------------|---------------------------------------------|------------------|-------|--------------------------------------------------|--------|--------|--------|------|

| Parameter                 |                                             | Symbol           | no.   | Condition                                        | Min.   | Тур.   | Max.   | Unit |

|                           | Output voltage                              | Vref             | 24    | Vref = 0 mA                                      | 3.465  | 3.500  | 3.535  | V    |

| Reference                 | Output voltage<br>temperature<br>regulation | ∆Vref<br>/Vref   | 24    | $Ta = -30^{\circ}C \text{ to } +85^{\circ}C^{*}$ |        | 0.5    | _      | %    |

| voltage block<br>(Ref)    | Input stability                             | Line             | 24    | Vcc = 4.6 V to 18 V                              |        | 1      | 10     | mV   |

| ()                        | Load stability                              | Load             | 24    | $I_0 = 0 \text{ mA to } -1 \text{ mA}$           |        | 3      | 10     | mV   |

|                           | Short circuit output current                | los              | 24    | VREF = 1 V                                       | -20    | -10    | -3     | mA   |

| Under voltage             | Threshold voltage                           | Vтн              | 4     | Vcc =                                            | 3.4    | 3.7    | 4.0    | V    |

| lockout circuit           | Hysteresis voltage                          | Vн               | 4     | —                                                |        | 0.18   | 0.21   | V    |

| block (UVLO)              | Reset voltage                               | Vrst             | 4     | —                                                | 1.7    | 2.1    | —      | V    |

| Soft start block<br>(CS)  | Charge current                              | Ics              | 4     | _                                                | -2.8   | -2.0   | -1.2   | μA   |

| Short circuit             | Threshold voltage                           | Vтн              | 4     | —                                                | 0.63   | 0.68   | 0.73   | V    |

| protection                | Input source current                        | ICSCP            | 22    | _                                                | -2.8   | -2.0   | -1.2   | μΑ   |

| comparator block<br>(SCP) | Short detection interval                    | tscp             | 22    | CSCP = 2200 pF                                   | 0.50   | 0.75   | 1.34   | ms   |

| Triangular wave           | Oscillator frequency                        | fosc             | 8, 11 | R <sub>T</sub> = 130 kΩ                          | 180    | 200    | 220    | kHz  |

| oscillator block<br>(OSC) | Frequency<br>temperature<br>regulation      | ∆f/fdt           | 8, 11 | Ta = −30°C to +85°C*                             | _      | 1      | _      | %    |

|                           | Threshold voltage                           | V <sub>TH1</sub> | 6     | FB = 1.6 V,<br>VD3 to VD0 = 1000                 | 1.5810 | 1.6000 | 1.6192 | V    |

|                           |                                             | V <sub>TH2</sub> | 6     | FB = 1.6 V,<br>VD3 to VD0 = 1110                 | 1.2845 | 1.3000 | 1.3156 | V    |

|                           | VTH temperature regulation                  | ΔVτ/Vτ           | 6     | Ta = -30°C to +85°C*                             |        | 0.5    |        | %    |

| Error amplifier           | Input bias current                          | Ів               | 5     | -IN = 0 V                                        | -200   | -50    | —      | nA   |

| block (Error<br>Amp.)     | Voltage gain                                | Av               | 6     | DC                                               | 60     | 100    | —      | dB   |

|                           | Frequency<br>bandwidth                      | BW               | 6     | $A_V = 0 dB^*$                                   | _      | 800    | _      | kHz  |

|                           | Output voltage                              | Vон              | 6     | _                                                | 2.18   | 3.5    | —      | V    |

|                           |                                             | Vol              | 6     | —                                                |        | 0.8    | 1.0    | V    |

|                           | Output source<br>current                    | ISOURCE          | 6     | FB = 1.6 V                                       |        | -90    | -45    | μΑ   |

|                           | Output sink current                         | Isink            | 6     | FB = 1.6 V                                       | 3.0    | 12.0   | _      | mA   |

\* : Standard design value

$(Ta = +25^{\circ}C, Vcc = 5 V)$

|                                                  |                                                    |        | Dia        |                                                      | (1a = +25°C, Vcc<br>Value |              |              |      |

|--------------------------------------------------|----------------------------------------------------|--------|------------|------------------------------------------------------|---------------------------|--------------|--------------|------|

| Para                                             | ameter                                             | Symbol | Pin<br>no. | Condition                                            |                           |              | Mov          | Unit |

|                                                  |                                                    |        | 110.       |                                                      | win.                      | Тур.         | Max.         |      |

| PWM comparator<br>blocks (PWM                    | Threshold voltage                                  | Vtl    | 8, 11      | Duty cycle = 0%                                      | 1.2                       | 1.3          |              | V    |

| Comp.1, 2)                                       |                                                    | Vтн    | 8, 11      | Duty cycle = Dtr                                     | —                         | 1.86         | 2.0          | V    |

| Dead time control<br>block (DTC)                 | Maximum duty cycle                                 | Dtr    | 8          | R⊤ = 130 kΩ                                          | 85                        | 90           | 95           | %    |

|                                                  | Output voltage                                     | Vон1   | 8          | OUT1 = -100 mA,<br>VB = 5 V, CB = 20 V,<br>VS = 15 V | CB – 2.5                  | CB – 1.5     | _            | V    |

| Output blocks                                    | (main side)                                        | Vol1   | 8          | OUT1 = 100 mA,<br>VB = 5 V, CB = 20 V,<br>VS = 15 V  | _                         | VS + 1.1     | VS + 1.4     | V    |

| (Drive1, 2)                                      | Output voltage<br>(synchronized<br>rectifier side) | Vон2   | 11         | OUT2 = -100 mA,<br>VB = 5 V                          | VB – 2.5                  | VB – 1.5     | _            | V    |

|                                                  |                                                    | Vol2   | 11         | OUT2 = 100 mA,<br>VB = 5 V                           | _                         | 1.1          | 1.4          | V    |

|                                                  | Diode voltage                                      | VDIODE | 13         | Idiode = 10 mA                                       |                           | 1.0          | 1.1          | V    |

|                                                  | CTL input voltage                                  | VIH    | 24         | IC operating mode                                    | 2.0                       |              | 18           | V    |

| Control block<br>(CTL)                           |                                                    | VIL    | 24         | IC standby mode                                      | 0                         |              | 1.0          | V    |

| (0.2)                                            | Input current                                      | Іст∟   | 19         | CTL = 5 V                                            |                           | 100          | 160          | μΑ   |

|                                                  | Threshold voltage                                  | Vtlow  | 21         | VD3 to VD0 setting,<br>VSENSE = _                    | 0.88<br>× VD              | 0.90<br>× VD | 0.92<br>× VD | V    |

| PWRGOOD<br>comparator                            |                                                    | Vтніgh | 21         | VD3 to VD0 setting,<br>VSENSE = _                    | 1.08<br>× VD              | 1.10<br>× VD | 1.12<br>× VD | V    |

| protection block<br>(PWRGD)                      | Hysteresis voltage                                 | Vн     | 21         | —                                                    | 3                         | 30           | 50           | mV   |

|                                                  | Output leak current                                | ILEAK  | 21         | PWRGOOD = 5 V                                        |                           | _            | 40           | μΑ   |

|                                                  | Output voltage                                     | Vol    | 21         | PWRGOOD = 1 mA                                       | —                         | 0.06         | 0.4          | V    |

| Discharge control<br>comparator (CS<br>Comp.)    | Threshold voltage                                  | Vтн    | 24         | CS = 7_                                              |                           | 0.05         | 0.07         | V    |

|                                                  |                                                    | Vін    | 24         | Discharge control ON                                 | 2.0                       |              | 18           | V    |

| Discharge control<br>ON/OFF block<br>(CTL LOGIC) | ENB input voltage                                  | VIL    | 24         | Discharge control<br>OFF                             | 0                         |              | 1.0          | V    |

|                                                  | Input current                                      | IENB   | 7          | ENB = 0 V                                            | -1.0                      | -0.05        | —            | μA   |

(Continued)

(Continued)

(Ta = +25°C, Vcc = 5 V)

| Dan                            | Ourseland                   | Pin        | O an ditian | Value                   |              |               | L los it     |      |

|--------------------------------|-----------------------------|------------|-------------|-------------------------|--------------|---------------|--------------|------|

| Para                           | ameter                      | Symbol no. |             | Condition               | Min.         | Тур.          | Max.         | Unit |

| Over voltage                   | Threshold voltage           | Vтн        | 8, 11       | VSENSE =,<br>VD = 1.3 V | 1.15<br>× VD | 1.175<br>× VD | 1.20<br>× VD | V    |

| protection<br>comparator block | Hysteresis voltage          | Vн         | 8, 11       | —                       | 3            | 30            | 50           | mV   |

| (OVP)                          | VSENSE pin input<br>current | Isense     | 20          | VSENSE = 0 V            | -10          | -0.1          | _            | μΑ   |

|                                | D/A input voltage           | Vih        | 14 to<br>17 | _                       | 2.0          | _             | 18           | V    |

| D/A (VD3 to VD0<br>pin) (D/A)  | D/A input voltage           | VIL        | 14 to<br>17 | _                       | 0            | _             | 1.0          | V    |

|                                | Input current               | lо         | 14 to<br>17 | VD3 to VD0 = 5 V        | _            | 0.05          | 1.0          | μΑ   |

| General                        | Standby current             | Iccs       | 23          | CTL = 0 V               | —            | _             | 10           | μA   |

|                                | Power supply current        | Icc        | 23          |                         | _            | 4.0           | 6.0          | mA   |

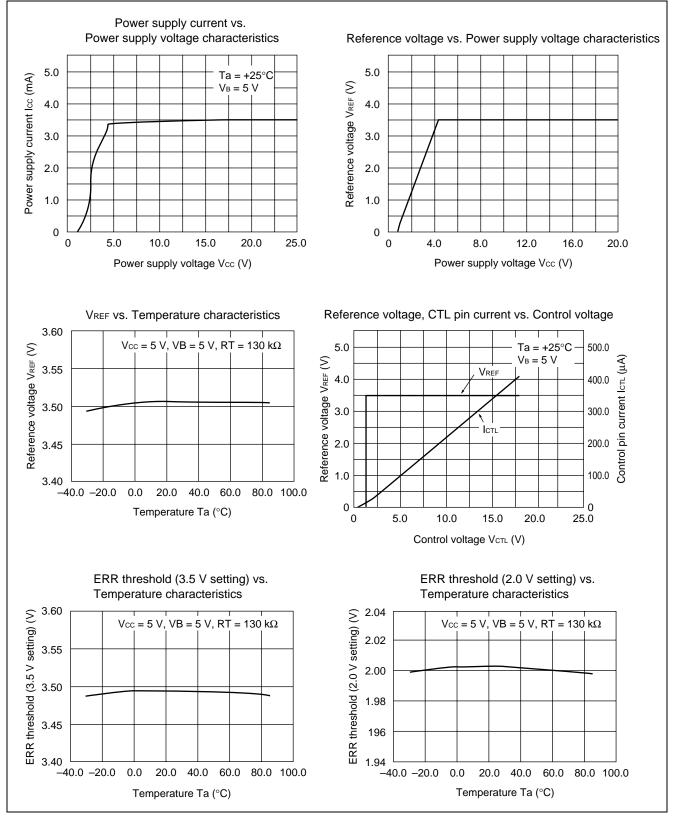

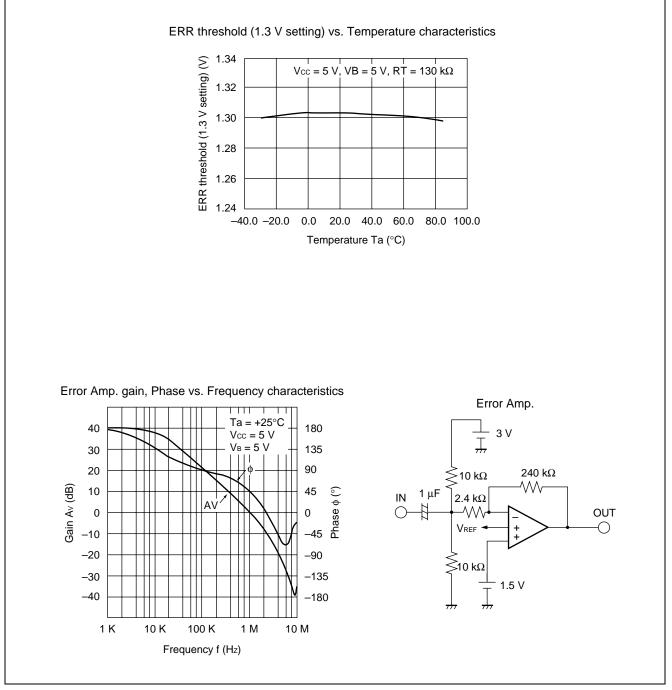

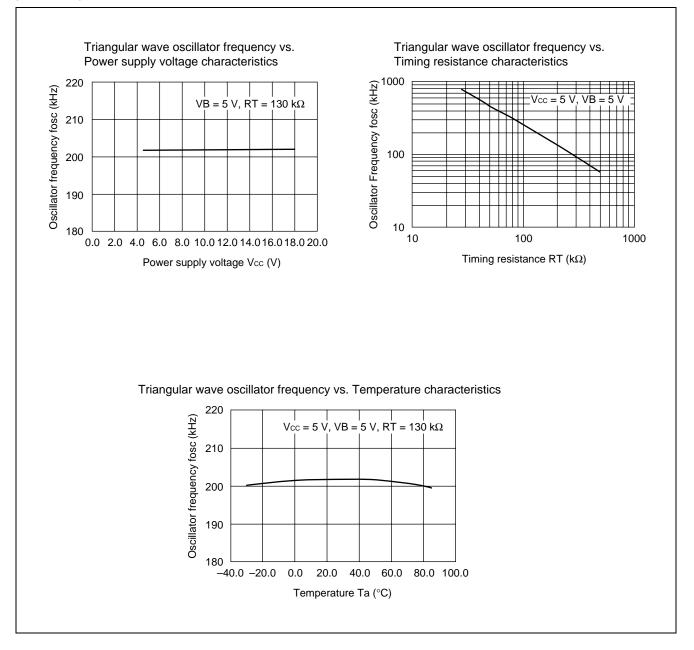

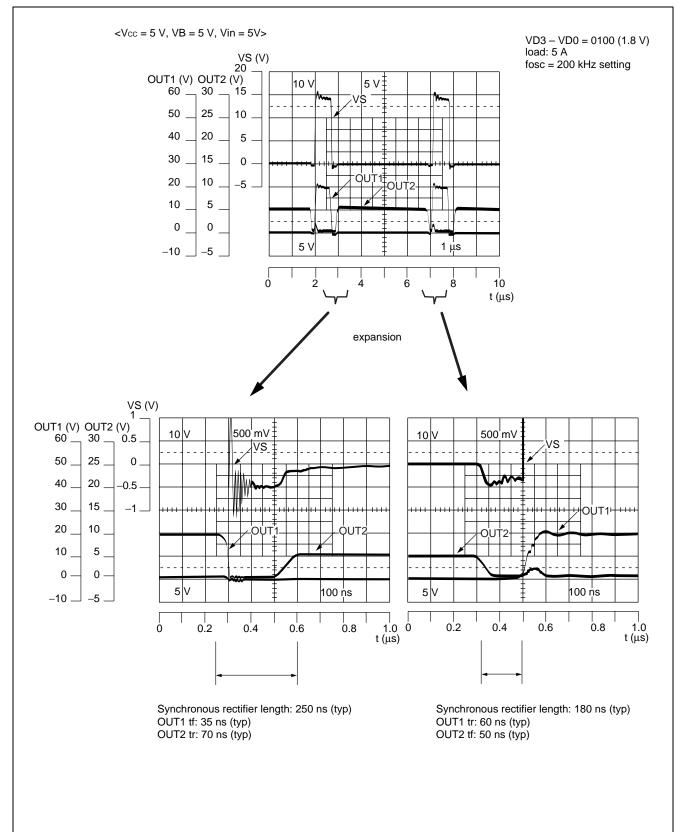

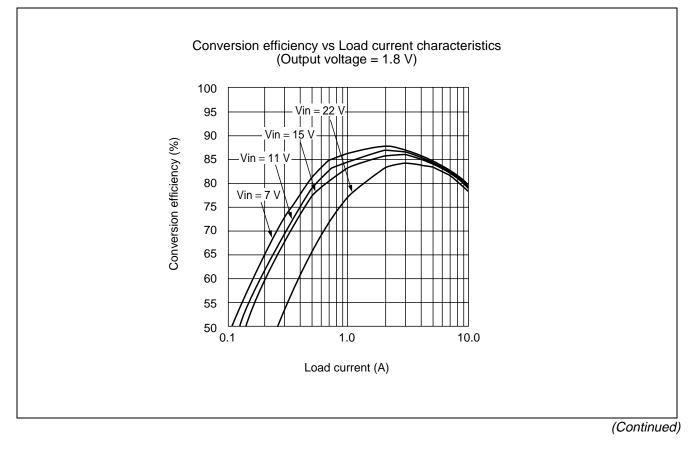

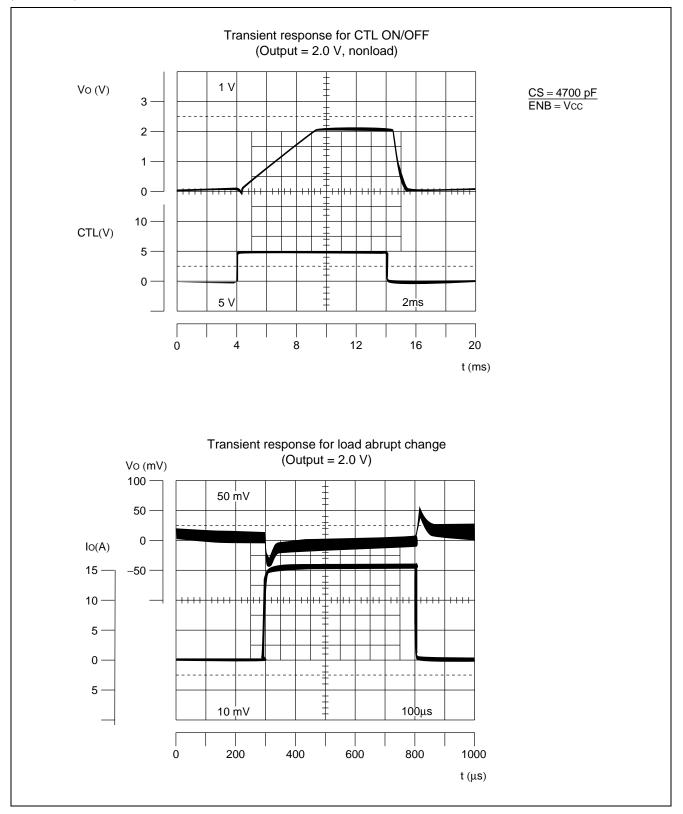

### ■ TYPICAL CHARACTERISTICS

<sup>(</sup>Continued)

#### (Continued)

(Continued)

#### (Continued)

## ■ FUNCTION DESCRIPTION

#### 1. Switching Regulator Function

#### (1) Reference voltage circuit (Ref)

The reference voltage circuit uses the voltage supply from the V<sub>CC</sub> pin (pin 23) to generate a temperature compensated reference voltage ( $\cong$  3.5 V) for use as the reference voltage for the internal circuits of the IC chip.

It is also possible to supply a reference voltage output of up to 1 mA to external circuits through the VREF pin (pin 24).

#### (2) Triangular wave oscillator (OSC)

The triangular wave form is generated using an on-chip frequency selection capacitor, plus the frequency selection resistance connected to the RT pin (pin 1).

The triangular wave is input to the PWM comparator circuits on the IC.

#### (3) Error amplifier (Error Amp.)

The error amplifier circuit is used to detect the output voltage from the DC/DC converter for output as the PWM control signal. The in-phase input range covers the full range from 0 V to  $V_{CC} - 0.9 \text{ V}$ . By connecting a feedback resistance and capacitor between the FB pin (pin 6) and -IN pin (pin 5), it is possible to create any desired level of loop gain, thereby providing stable phase compensation to the system.

Also, it is possible to prevent current spikes at power supply start-up by connecting a soft start capacitor to the CS pin (pin 4), the non-inverting input pin for Error Amp. The use of Error Amp. for soft start detection makes it possible for a system to operate on a fixed soft start time that is independent of the output load on the DC/ DC converter.

#### (4) PWM comparators (PWM Comp.1, PWM Comp.2)

PWM Comp.1 and PWM Comp.2 are voltage-pulse width converters that control output voltage according to input voltage.

PWM Comp.1 controls the pulse width on the main-side output circuit, and PWM Comp.2 controls the pulse width on the synchronous rectifier side output circuit.

The triangular wave generated by the triangular wave oscillator is compared with the output voltage from Error Amp., and during intervals when Error Amp. output is higher than the triangular wave, the main-side output transistor is switched on and the synchronous rectifier side output transistor is turned off.

PWM Comp.1 is set to a maximum duty cycle of approximately 90%.

#### (5) Output circuits (Drive1, Drive2)

The output circuits on both the main-side and synchronous rectifier-side have a totem-pole configuration, and are capable of driving an external N-ch. MOS FET.

#### (6) Power supply control circuit (CTL)

This circuit is able to control power supply ON/OFF switching from the CTL pin (pin 19). (During standby mode, supply current is 0  $\mu$ A TYP.)

#### (7) DAC circuit (D/A)

This circuit controls the output voltage fed to the CPU; using 4-bit input information allows the voltage to be selected in 50 mV steps from 1.3 V to 2.0 V.

When all D/A input pins VD3 through VD0 (pin 17 through pin 14) are set to "H" level, DC/DC converter output voltage is 0 V.

#### 2. Protection Functions

#### (1) Vcc under voltage lockout circuit (UVLO)

Power surges at power-on, or momentary under-voltage situations can cause abnormal operation in the MB3871, which may lead to damage or deterioration in systems. This circuit prevents abnormal operation during times of low voltage by using the supply voltage to detect the level of the internal reference voltage, and fixes output pins OUT1 (pin 8) and OUT2 (pin 11) to "L" level. Once the supply voltage recovers to a level above the threshold voltage of the under voltage lockout circuit, operation is restored.

#### (2) Timer-latch short-circuit protection circuit (SCP)

This circuit detects the output voltage level from Error Amp. and activates the timer circuit, charging the external capacitor from the CSCP pin (pin 22) when Error Amp. output voltage level reaches or exceeds about 2.1 V. If Error Amp. output does not return to the normal voltage range before the capacitor voltage reaches about 0.68 V, the latch circuit is activated and the output pins (OUT1, OUT2) are held at "L" level. Once the protector circuit is activated, it can be reset by switching the power supply off and on again.

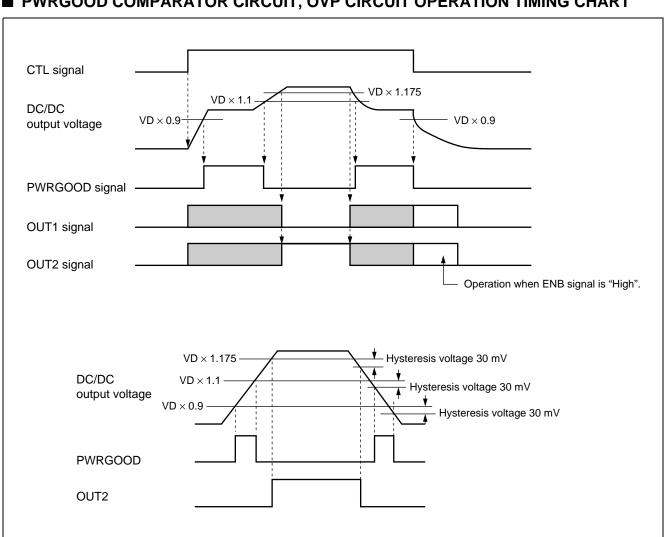

#### (3) Overvoltage protection circuit (OVP)

When the DC/DC converter output voltage (V<sub>o</sub>) exceeds the output voltage set by the VD3 to VD0 pins by more than +17.5%, the overvoltage protection circuit output signal goes to "H" level causing one output pin (OUT1) to be held at "L" level and the other output pin (OUT2) to be held at "H" level.

#### (4) PWRGOOD comparator detection circuit (PWRGD)

The PWRGOOD pin (pin 21) outputs an "H" level signal as long as the VSENSE pin (pin 20) is receiving the DC/DC converter output voltage (Vo) within the range of 0.9 to 1.1 times the output voltage set by the VD3 to VD0 pins.

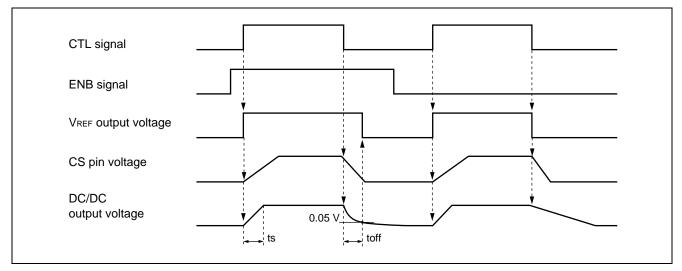

#### 3. Soft Start/Discharge Control

#### (1) Soft start circuit (CS)

Connecting a capacitor to the CS pin (pin 4) prevents the inrush current at power turnon. Using an Error Amp. for detecting the soft error allows the soft start time to be initiated independent of output load from the DC/DC converter.

#### (2) Discharge control ON/OFF circuit (CTL LOGIC)

Entering an "L" level signal at the CTL pin while an "H" level signal is input at the ENB pin causes the discharge control ON/OFF circuit (CTL LOGIC) to switch the soft start circuit (CS) from charging to discharging.

The resistance (Rs) connected to the RS pin (pin 2) charges the soft start capacitor (Cs), so that Error Amp. provides control over the DC/DC converter output voltage in the same way as during a soft start. This makes it possible to control voltage drop independently of output load.

When the CS pin voltage reaches the discharge control comparator circuit (CS Comp.) threshold voltage ( $\cong$  50 mV), the discharge control is canceled.

When an "L" level signal is input at the ENB pin (pin 7), the DC/DC converter output voltage discharge time control is switched OFF.

### METHOD OF SETTING THE SOFT START TIME

At startup of the MB3871, the capacitor (Cs) connected to the CS pin begins charging. This produces a soft start, by providing output voltage from Error Amp. that is proportional to the CS pin voltage regardless of the DC/DC converter load current.

Soft start time (time to output setting voltage VD)

ts (sec)

$$\simeq \frac{VD}{2 (\mu A)} \times Cs (\mu F)$$

#### TIME SETTING BY SHORT DETECTION

When load conditions change rapidly with the reduced output voltage, as when a load fault occurs, the Capacitor Cscp connected to the CSCP pin (pin 22) is charged to threshold voltage ( $V_{TH}$ :=0.68V) and sets a latch, the external FET is turned off (inactive interval 100%).

Short detection time

tpe (sec)  $\simeq 0.68 \times C_{\text{SCP}} \left( \mu F \right)$  / 2 ( $\mu A$ )

### OSCILLATOR FREQUENCY SETTING

The oscillator frequency can be set by connecting resistance to the RT pin (pin 1).

Oscillator frequency

fosc (kHz)  $\simeq$  26250 / RT (k $\Omega$ )

### ■ METHOD OF SETTING THE DISCHARGE TIME

• An "L" level CTL signal while the ENB pin is set to "H" level causes the resistance (Rs) connected to the RS pin to discharge electrical charge the capacitor (Cs) connected to the CS pin, causing the output voltage to fall gradually regardless of the DC/DC converter load current.

Discharge time (time to 0.05 V output voltage)

$\text{toff (msec)} \simeq R_{\text{S}} \left( k\Omega \right) \times C_{\text{S}} \left( \mu F \right) \times \text{In} \left( \frac{\text{VD}}{\text{V}_{\text{TH (CS COMP)}}} \right)$

• As long as the ENB pin is set to "L" level, the discharge control function is switched OFF.

### D/A BLOCK VD3 to VD0 SWITCHING

- Switching of the VD3 to VD0 pin signal during the MB3871 operation may cause transient fluctuation in output voltage from the DC/DC converter. The resulting voltage instability may cause an "L" level from the PWRGOOD block, activating the OVP protection and shutting off the output from the DC/DC converter.

To switch VD3 to VD0 pin settings, first input an "L" level control signal to the CTL pin to place the MB3871 in standby status.

- When all VD3 to VD0 pin signals are set to "H" level, the DC/DC converter output is switched OFF.

# ■ PWRGOOD COMPARATOR CIRCUIT, OVP CIRCUIT OPERATION TIMING CHART

# ■ CTL LOGIC CIRCUIT OPERATION TIMING CHART

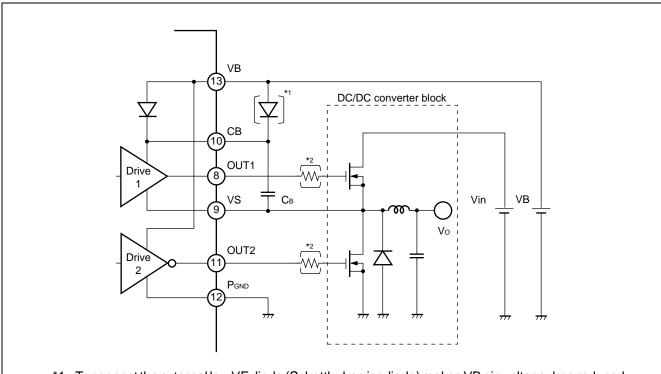

## ■ DC/DC CONVERTER INPUT VOLTAGE (Vin) AND VB VOLTAGE SETTING

The voltage at the CB pin is bootstrapped from the VS pin voltage by an amount equivalent to the VB pin voltage, as a result of the bootstrap capacitance ( $C_B$ ) between the CB pin and VS pin. Therefore, either the Vin voltage or VB pin voltage should be adjusted so that the sum of the DC/DC converter block input voltage Vin plus the VB pin voltage does not exceed the recommended operating conditions for the CB pin boot voltage ( $V_{CB}$ ).

- \*1: To connect the external low VF diode (Schottky barrier diode) makes VB pin voltage drop reduced and then can perform the higher efficiency.

- \*2: The switching noise can be reduced ( $0\Omega$  to  $5\Omega$ ) by connecting the resistance when the external MOSFET gate input capacitance (Ciss) is large, caused by the external MOSFET gate drive current limiting resistance.

## ■ APPLICATION EXAMPLE

# ■ REFERENCE DATA

(Continued)

### USAGE PRECAUTIONS

#### 1. Device settings must not exceed absolute maximum ratings.

Usage under conditions exceeding absolute maximum ratings may permanently damage LSI devices.

Note also that in normal operation usage within recommended operating conditions is preferred, and that the reliability of LSI devices may be adversely affected when used outside these conditions.

#### 2. Devices should be used within recommended operating conditions.

Recommended operating conditions are recommended values within which the LSI device is warranted to operate normally.

Rated values of electrical characteristics are warranted within the range of recommended operating conditions and within the conditions listed in the condition column for each parameter.

3. Printed circuit board ground lines should be designed in consideration of common impedance values.

#### 4. Observe precautions against static electricity.

- Containers in which semiconductors are placed should either be protected against static electricity, or be of conductive material.

- After mounting of devices, use conductive bags or conductive containers when storing or transporting printed circuit boards.

- Working surfaces, tools and instruments should be properly grounded.

- Workers should be grounded by a ground line with 250 k $\Omega$  to 1 M $\Omega$  resistance in series between the worker and ground.

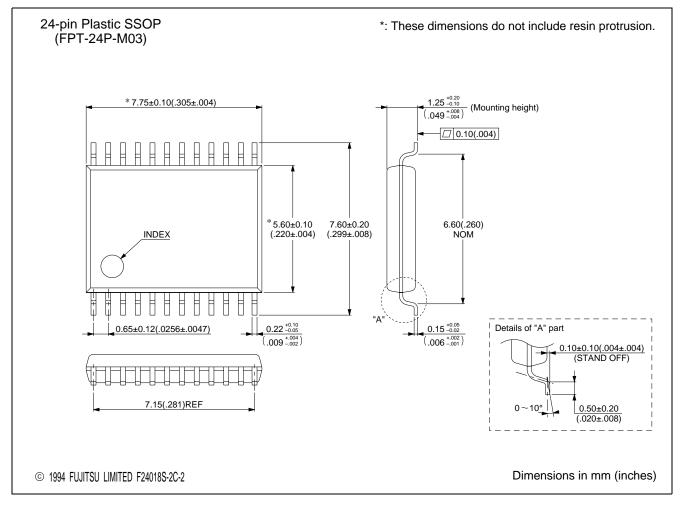

#### ORDERING INFORMATION

| Part number      | Package                              | Remarks |

|------------------|--------------------------------------|---------|

| MB3871 PFV-G-BND | 24-pin Plastic SSOP<br>(FPT-24P-M03) |         |

■ PACKAGE DIMENSION

# FUJITSU LIMITED

For further information please contact:

#### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-8588, Japan Tel: 81(44) 754-3763 Fax: 81(44) 754-3329

http://www.fujitsu.co.jp/

#### North and South America

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, USA Tel: (408) 922-9000 Fax: (408) 922-9179

Customer Response Center *Mon. - Fri.: 7 am - 5 pm (PST)* Tel: (800) 866-8608 Fax: (408) 922-9179

http://www.fujitsumicro.com/

#### Europe

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag Germany Tel: (06103) 690-0 Fax: (06103) 690-122

http://www.fujitsu-ede.com/

#### Asia Pacific

FUJITSU MICROELECTRONICS ASIA PTE LTD #05-08, 151 Lorong Chuan New Tech Park Singapore 556741 Tel: (65) 281-0770 Fax: (65) 281-0220

http://www.fmap.com.sg/

F9903 © FUJITSU LIMITED Printed in Japan

#### All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.). CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.